# A Pulsed Power Supply Adopting Active Capacitor Converter for Low-Voltage and Low-Frequency Pulsed Load

Xinze Huang, Student Member, IEEE, Xinbo Ruan, Fellow, IEEE, Fangjun Du, Fei Liu, Li Zhang, Student Member, IEEE

Abstract—In a dc pulsed power supply (PPS), its instantaneous output power is pulsed, and its input power is required to be constant. In order to balance the instantaneous power difference, a storage capacitor is usually connected to the output terminal of the PPS. However, the storage capacitor is extremely large when the pulse repetition frequency is relatively low. In this paper, an active capacitor converter (ACC) is adopted in place of the storage capacitor. In the ACC, the storage capacitor is greatly reduced by intentionally increasing its voltage ripple. To improve the tracking ability of the terminal current of the ACC, a current reference feed-forward control scheme is proposed, and it is further simplified for avoiding the use of the reciprocal and square root circuits. In order to improve the dynamic response of the PPS when the pulsed load is triggered on and terminated, several methods are proposed. The methods of imposing a negative dc bias on the current reference and peak voltage control for the ACC storage capacitor are aiming for reducing the undershoot and overshoot of the output voltage, and two fast voltage loops are incorporated for limiting the maximum and minimum voltage of the storage capacitor in the ACC. Finally, a prototype with the output peak power of 2 kW, the output average power of 300 W, and the pulse repetition frequency of 150 Hz ~ 300 Hz is fabricated and tested to verify the validity of proposed PPS and control schemes.

*Index Terms* — Pulsed power supply, active capacitor converter, tracking ability, current reference feed-forward scheme, peak voltage control.

## I. INTRODUCTION

**P** ulsed power supply (PPS) is one kind of special power supplies, which outputs periodical voltage or current with rectangular wave, triangular wave or trapezoidal wave, and it has been widely used in electrostatic precipitation [1], electroplating [2], pulse electrochemical wastewater treatment [3], [4] and radar transmitter [5]–[7]. According to the pulse repetition frequency (PRF), the PPS can be categorized into two types: high-frequency PPS and low-frequency PPS. The PPS can also be classified into high-voltage PPS and low-voltage PPS according to its output voltage level. In this paper, a high-power, low-frequency, low-voltage, and rectangular-wave PPS is studied, which outputs pulsed current with constant voltage.

As an interface between the power source and the pulsed load, the PPS should meet the following requirements:

The authors are with the Center for More-Electric-Aircraft Power System, the College of Automation Engineering, Nanjing University of Aeronautics and Astronautics, Nanjing 211106, China (e-mail: huangxinze@nuaa.edu.cn; ruanxb@nuaa.edu.cn; gmdufj@nuaa.edu.cn; fayliu@nuaa.edu.cn; zhangli\_frank @ nuaa.edu.cn).

1) The input current of the PPS is constant so that the low-frequency pulsed current does not propagate to the power source, which is especially important for photovoltaic panels to achieve high energy conversion efficiency and for fuel cells to extend its lifespan [8]–[10]; 2) When the pulsed load is being powered, the output voltage drop during the pulse cycle is small enough to ensure proper operation of the pulsed load [6], [7]; and 3) The PPS has high power density, which is very important, especially for the volume-critical and weight-critical applications. With constant output voltage and pulsed output current, the instantaneous output power of the PPS is pulsed. Meanwhile, the input current is required to be constant, thus the input power of the PPS is expected to be flat. To balance the instantaneous power difference, a storage capacitor is usually connected at the output terminal of the PPS. However, if the PRF is low, very large storage capacitors are required to achieve a small output voltage drop during the pulse cycle, leading to large size and heavy weight, and thus a low power density.

A bidirectional converter could be employed in place of the large storage capacitor for balancing the instantaneous input and output power difference, and it has been widely used in single-phase dc-ac inverters [11]-[14] and single-phase power factor correction (PFC) rectifiers [14]–[21]. By intentionally increasing the voltage ripple of the storage capacitor in the bidirectional converter, the storage capacitor could be significantly reduced. In voltage regulator (VR), a bidirectional converter is used to mitigate the voltage swing during the transients [22]-[24]. In addition, a bidirectional converter named adaptive active capacitor converter (AACC) is introduced for emulating a variable capacitor to stabilize the cascaded dc-dc converter system [25]. And the concept of the emulated variable capacitor is also presented in [26] and [27] to replace inflexible passive capacitors. Basically, the bidirectional converters mentioned above is to replace the undesired bulky capacitor and create an extra path for the unbalanced power. This approach can be also applied to the PPS, and the bidirectional converter is named active capacitor converter (ACC), which has been presented in [28]. This paper will provide more detailed design considerations for the PPS adopting the ACC.

The primary control objective of the ACC is to regulate its terminal current to provide the pulsed current except the dc component. A dual-loop control method is proposed in [20] for the ACC in LED driver (single-phase PFC rectifier) where the output current of the PFC converter is sinusoidal with twice the line frequency. In this method, a current loop is introduced to control the terminal current of the ACC and make it equal to the ac component of the output current of the PFC converter, and a voltage loop is used to regulate the voltage of the ACC storage capacitor. To improve the ACC terminal current tracking ability, a feed-forward control scheme is proposed in [21], in which the instantaneous expression of the duty cycle is calculated. Unfortunately, to

Manuscript received September 12, 2017; revised December 10, 2017; accepted January 9, 2018. This work was supported by the National Science Foundation of China for Distinguished Young Scholars under Award 51525701. Recommended for publication by Associate Editor XXX.

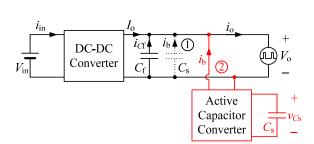

Fig. 1. Circuit configuration of the PPS with different locations of the storage capacitor.

realize the feed-forward function, an analog multiplier must be included to implement the reciprocal circuit and square root circuit, which makes the control circuit quite complicated.

For the PPS studied in this paper, the load current is rectangular, and it contains abundant harmonics at PRF and its multiples. In order to improve the tracking ability of the ACC terminal current, the feed-forward control scheme proposed in [21] is modified for the applications with an arbitrary load current in this paper. Furthermore, the expression of the duty cycle is linearized by applying the Taylor's approximation. In doing so, the multiplier can be removed and the control circuits can be simplified.

This paper is organized as follows. In Section II, the circuit configuration of the PPS is presented. The feed-forward control scheme for the ACC with an arbitrary load current is derived and simplified in Section III. The dynamic response of the PPS is analyzed and the methods for improving the dynamic response are given in Section IV. In Section V, the design of the ACC inductor and the output filter capacitor of the dc-dc converter are discussed. In Section VI, the experimental results from a prototype with output peak power of 2 kW, output average power of 300 W, and PRF of 150 Hz  $\sim$  300 Hz are provided to verify the proposed control scheme. Finally, Section VII concludes this paper.

#### II. CIRCUIT CONFIGURATION OF THE PPS

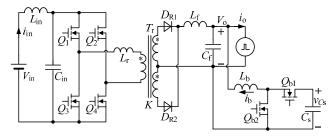

Fig. 1 shows the circuit configuration of the PPS, where the dc-dc converter converts the input dc voltage  $V_{in}$  to the desired dc output voltage  $V_{0}$ . The bandwidth of the dc-dc converter is generally designed to be quite low for the purpose of preventing the low-frequency pulsed output current from propagating to the input voltage source [29], [30]. In order to handle the pulsed power, a large storage capacitor,  $C_{\rm s}$ , is directly connected in parallel with the output terminal of the PPS. The large storage capacitor can also be replaced by an ACC. Certainly, a storage capacitor is still required in the ACC. Noted that  $C_{\rm f}$  is the output filter capacitor of the dc-dc converter to filter the switching-frequency current.

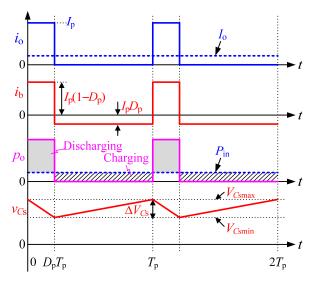

Fig. 2 shows the key operational waveforms of the PPS. The pulsed output current  $i_0$  is a rectangular waveform, where,  $I_p$  is the magnitude,  $T_p$  is the pulse repetition period,  $D_p$  is the pulse duty cycle, and  $I_0$  is the average output current. Since the output voltage  $V_0$  is constant, the instantaneous output power is pulsed. As mentioned above, the input current of the PPS,  $i_{in}$ , is expected to be controlled to be flat, so the input power of the PPS,  $P_{in}$ , is constant.  $i_b$  is the current provided by the storage capacitor.

No matter the storage capacitor is located at the output terminal or within the ACC, when  $P_{in} > p_0$ , the superfluous energy will charge the storage capacitor, and the storage capacitor voltage  $v_{Cs}$  increases; while when  $P_{in} < p_0$ , the

Fig. 2. Key operational waveforms of the PPS.

storage capacitor is discharged to provide the deficit, and  $v_{Cs}$  decays.

According to Fig. 2, the energy absorbed by the storage capacitor during one pulse cycle is

$$\Delta E_{Cs} = V_{o} D_{p} I_{p} \left( 1 - D_{p} \right) T_{p} \tag{1}$$

$\Delta E_{Cs}$  can be also expressed as

$$\Delta E_{Cs} = \frac{1}{2} C_s V_{Cs\,max}^2 - \frac{1}{2} C_s V_{Cs\,min}^2 \tag{2}$$

where  $V_{Csmax}$  and  $V_{Csmin}$  are maximum and minimum voltages of the storage capacitor, respectively.

From (1) and (2), the capacitance of the storage capacitor can be derived as

$$C_{s} = \frac{2V_{o}I_{p}D_{p}(1-D_{p})}{f_{p}(V_{Cs\,m\,ax}^{2}-V_{Cs\,min}^{2})}$$

$$= \frac{V_{o}I_{p}D_{p}(1-D_{p})}{f_{p}(V_{Cs\,m\,ax}-V_{Cs\,min})(V_{Cs\,m\,ax}+V_{Cs\,min})/2}$$

$$= \frac{V_{o}I_{p}D_{p}(1-D_{p})}{f_{p}\cdot\Delta V_{Cs}\cdot V_{Cs,ave}}$$

(3)

where,  $f_p = 1/T_p$  is the PRF,  $\Delta V_{Cs} = V_{Csmax} - V_{Csmin}$  is the voltage ripple across  $C_s$ ,  $V_{Cs\_ave} \approx (V_{Csmax} + V_{Csmin})/2$  is the average voltage of  $C_s$ . As seen from (3), the capacitance of the storage capacitor can be significantly reduced by intentionally increasing  $V_{Cs\_ave}$  and/or  $\Delta V_{Cs}$ .

Here, we take the PPS with 2 kW peak output power as an example to illustrate the design of the capacitance of the storage capacitor. Table I gives the key specifications of the PPS. When the storage capacitor is connected at the output terminal of the PPS, by substituting  $V_{cs\_ave} = V_o = 28 \text{ V}, \Delta V_{Cs} = 28 \text{ V} \times 3\%, f_p = 150 \text{ Hz}, D_p = 15\%, I_p = 71 \text{ A into (3), it can be calculated that the required storage capacitor <math>C_s = 71.85 \text{ mF.}$

When the ACC is adopted, a large voltage ripple on  $C_s$  is allowed since it is not restricted by the voltage drop during the pulse cycle. Letting  $V_{Cs ave} = 48$  V,  $\Delta V_{Cs} = 24$  V and substituting them together with  $f_p = 150$  Hz,  $D_p = 15\%$ ,  $V_o = 28$ V,  $I_p = 71$ A into (3), the required capacitance of the ACC storage capacitor is 1.47 mF, which is only 2.04% of the storage capacitance connected at the output terminal. Apparently, the storage capacitance could be significantly reduced when the ACC is adopted. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2018.2793187, IEEE Transactions on Power Electronics

| TABLE I                       |

|-------------------------------|

| KEY SPECIFICATIONS OF THE PPS |

| Parameters                                        | Value          |

|---------------------------------------------------|----------------|

| Input voltage $V_{\rm in}$ / V                    | 100            |

| Output Voltage $V_{\rm o}$ / V                    | 28             |

| Output peak current $I_p / A$                     | 71             |

| Pulse repetition frequency $f_p$ / Hz             | $150 \sim 300$ |

| Pulse duty cycle $D_{\rm p}$                      | $\leq 15\%$    |

| Allowed maximum output voltage drop $\Delta V_o$  | 3%             |

| Allowed minimum input current $\Delta I_{in} / A$ | 0.5            |

## III. PROPOSED CURRENT REFERENCE FEED-FORWARD CONTROL SCHEME FOR THE ACC

The dc-dc converter and the ACC are independently controlled. The control objective of the dc-dc converter is to restrain the low-frequency ripple in the input current of the dc-dc converter while regulating the output voltage. Various control strategies for the dc-dc converter have been discussed and compared in [29] and [30]. In this paper, a dual-loop control, which consists of an outer voltage loop and an inner filter inductor current loop, is employed for the dc-dc converter. By reducing the bandwidth of the outer voltage loop, the low-frequency ripple in the input current of the dc-dc converter can be reduced effectively. The design of the dual-loop control has been extensively discussed in previous publications, and it will not be repeated here.

## A. Current Reference Feed-Forward Control Scheme for the ACC

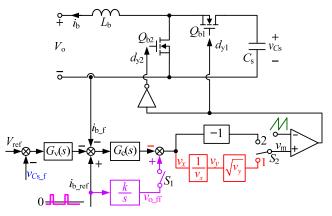

Fig. 3 gives the topology and control schematic diagram of the ACC. Here, the ACC is a boost converter from the view of the output terminal of the PPS. A voltage and current dual-loop control method is used for the ACC with switch  $S_1$ being opened and  $S_2$  being turned to terminal 2, which is proposed in [20]. The current loop aims for controlling the terminal current of the ACC to make it equals to the ac component of the load current, and the voltage loop is used to regulate the storage capacitor voltage of the ACC. The output of the voltage regulator is added to the current reference to compensate the circuit losses. In order to eliminate the influence of the output of the voltage regulator on the current reference, the bandwidth of the voltage loop should be designed to be far lower than the PRF, and the output of the voltage regulator is approximately a dc value.

Referring to Fig. 2, the rectangular-wave load current contains abundant harmonics at the PRF and its multiples. Hence, to ensure an excellent current tracking ability, the gain of the current loop at the PRF and its multiples should be designed as high as possible, i.e., the bandwidth of the current loop should be designed high enough. However, for ensuring the system stability, the current loop bandwidth cannot be too high, making it difficult to achieve satisfactory current tracking ability. A feed-forward control scheme is proposed in [21] to improve the current tracking ability, yet it is only applicable to cases where the load current is sinusoidal. In this paper, the feed-forward control scheme is modified for to the cases with an arbitrary load current, which will be presented as follows.

According to Fig. 2, the energy that discharges  $C_{\rm s}$  is

$$\Delta E_{Cs} = \int_0^t V_{\rm o} i_{\rm b} \left( t \right) dt \tag{4}$$

Fig. 3. Control schematic diagram of the ACC.

And  $\Delta E_{Cs}$  can be also expressed as

$$\Delta E_{C_{\rm S}} = \frac{1}{2} C_{\rm s} V_{C_{\rm S}\,{\rm max}}^2 - \frac{1}{2} C_{\rm s} v_{C_{\rm S}}^2(t) \tag{5}$$

Combining (4) and (5), the instantaneous voltage of  $C_{\rm s}$  can be derived as

$$v_{Cs}(t) = \sqrt{-\frac{2}{C_s} \int_0^t V_o \dot{i}_b(t) dt + V_{Cs\,m\,ax}^2}$$

(6)

According to (6), the desired instantaneous duty cycle of switch  $Q_{b1}$  can be calculated as

$$d_{yl}(t) = \frac{V_{o}}{v_{Cs}(t)} = \frac{V_{o}}{\sqrt{-\frac{2}{C_{s}}\int_{0}^{t}V_{o}i_{b}(t)dt + V_{Csmax}^{2}}}$$

(7)

The duty cycle of  $Q_{b1}$  is obtained by comparing the modulation signal with the sawtooth carrier signal. So, the needed modulation signal  $v_m(t)$  is

$$v_{\rm m}(t) = d_{\rm yl}(t)V_{\rm M} = \frac{V_{\rm o}V_{\rm M}}{\sqrt{-\frac{2}{C_{\rm s}}\int_{0}^{t}V_{\rm o}i_{\rm b}(t)dt + V_{C\rm s\,m\,ax}^{2}}}$$

$$= \frac{1}{\sqrt{k_{\rm l}\int_{0}^{t}i_{\rm b}(t)dt + k_{\rm 2}}}$$

(8)

where,  $V_{\rm M}$  is the amplitude of the saw-tooth carrier, and  $k_1$  and  $k_2$  are

$$k_{\rm I} = -\frac{2}{C_{\rm s}V_{\rm o}V_{\rm M}^2} \tag{9}$$

$$k_2 = \frac{V_{C_{\rm Smax}}^2}{V_{\rm o}^2 V_{\rm M}^2} \tag{10}$$

The terms  $k_1$  and  $k_2$  are constant when the parameters of the main circuits of the ACC are determined.

In order to produce the modulation signal according to (8) - (10) and incorporate it in the dual-loop control circuit, a feed-forward path and a calculation circuit, which consists of an integrator k/s, a reciprocal circuit and a square root circuit, is added, and then S<sub>1</sub> is closed and S<sub>2</sub> is turned to terminal 1, as shown in Fig. 3, where the term k is designed be equal to  $k_1$ . This is called the current reference feed-forward control scheme. It should be pointed out that the load current  $i_b(t)$  in (8) can be arbitrary while the feed-forward control scheme proposed in [21] is only for the load current with sinusoidal waveform. For realizing the reciprocal circuit and square root circuit, analog multiplier is required, which makes the control circuit more complicated.

*B.* Simplified Current Reference Feed-Forward Control Scheme for the ACC

Define

$$x = -\frac{2}{C_s} \int_0^t V_o i_b(t) dt + V_{C_s \max}^2$$

(11)

Then, (8) can be rewritten as

$$v_m(x) = \frac{V_o V_M}{\sqrt{x}}$$

(12)

By applying Taylor's expansion on  $1/\sqrt{x}$ ,  $1/\sqrt{x}$  can be approximated as

$$\frac{1}{\sqrt{x}} = -\frac{1}{2\sqrt{x_0^3}}x + \frac{3}{2\sqrt{x_0}}$$

(13)

where  $x_0 = (V_{Csmin}^2 + V_{Csmax}^2)/2$ . The detailed derivation procedure is given in the Appendix.

According to (11) to (13),  $v_m(t)$  can be approximated as

$$v_{m_{\text{fit}}}(t) = V_{\text{o}}V_{\text{M}} \left[ \frac{3}{2\sqrt{x_{0}}} - \frac{1}{2\sqrt{x_{0}^{3}}} \left( -\frac{2}{C_{\text{s}}} \int_{0}^{t} V_{\text{o}}i_{\text{b}}(t) dt + V_{C\text{smax}}^{2} \right) \right]$$

$$= V_{\text{o}}V_{\text{M}} \left[ \frac{1}{C_{\text{s}}\sqrt{x_{0}^{3}}} \int_{0}^{t} V_{\text{o}}i_{\text{b}}(t) dt + \frac{3}{2\sqrt{x_{0}}} - \frac{1}{2\sqrt{x_{0}^{3}}} V_{C\text{smax}}^{2} \right]$$

$$= k_{1}^{\prime} \int_{0}^{t} i_{\text{b}}(t) dt + k_{2}^{\prime}$$

where

$$c_1' = \frac{V_o^2 V_M}{C_s \sqrt{x_0^3}}$$

(15)

$$k_{2}' = V_{o}V_{M} \left( \frac{3}{2\sqrt{x_{0}}} - \frac{1}{2\sqrt{x_{0}^{3}}} V_{Cs\,\text{max}}^{2} \right)$$

(16)

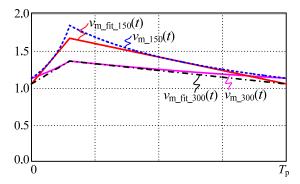

The terms  $k_1'$  and  $k_2'$  are constant when the parameters of the main circuits of the ACC are determined. By letting  $V_0 =$ 28 V,  $V_{Csmin} =$  35 V,  $V_{Csmax} =$  60 V,  $V_M =$  1.8 V and substituting them together with  $C_s =$  1.47 mF,  $D_p = 0.15$ ,  $f_p =$

k

150 Hz and  $f_p = 300$  Hz into (8) and (14), respectively, the curves of  $v_m(t)$  and  $v_{m_{i}fit}(t)$  are depicted in Fig. 4. Note that "150" and "300" in the subscript denote the PRF. As seen, the fitting error is small and acceptable, so it is reasonable to replace  $v_m(t)$  with  $v_{m_{i}fit}(t)$ .

In Fig. 3, when switch S<sub>1</sub> is closed and S<sub>2</sub> is turned to terminal 2, the control schematic diagram is for simplified current reference feed-forward control scheme, where, the term k is designed to be equal to  $-k_1'$ . The output of the current regulator can provide the term  $k_2'$  and the error between  $v_m(t)$  with  $v_{m_{\text{fif}}}(t)$ . Thus, the desired modulation signal shown as (8) can be obtained. As seen, the reciprocal circuit and square root circuit are no longer needed, leading to a simplified realization of the control circuit.

### C. Control Circuits for Implementation of the Current Reference Feed-Forward Control Scheme

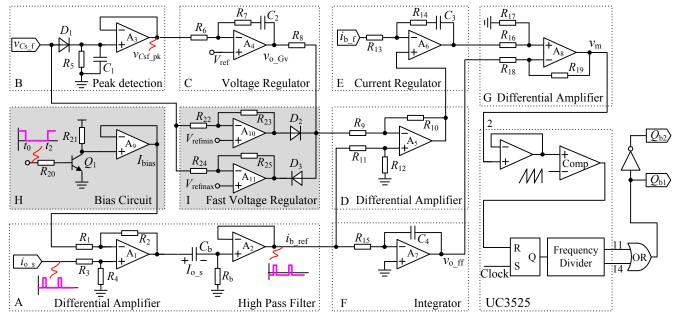

Based on previous analysis, Fig. 5 shows the detailed control circuit of the simplified current reference feed-forward control scheme, which are implemented by analog components.

In subcircuit A, the load current sampling signal  $i_{o_s}$  is first amplified by a differential amplifier comprising  $R_1 - R_4$ and amplifier A<sub>1</sub>. Then, the output of A<sub>1</sub> is sent to a one-order high-pass filter (HPF) composed of  $R_b$ ,  $C_b$  and amplifier A<sub>2</sub> to extract the ac component of the pulsed load current, defined as  $i_{b_ref}$ , which is taken as a part of the current reference of  $i_b$ .

Subcircuit B is a peak value detection circuit, composed

Fig. 4. Fitting curves of the modulation signals.

(14)

Fig. 5. Control circuit of the ACC.

0885-8993 (c) 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Subcircuit E is the current regulator, which is a PI regulator here, composed of  $R_{13}$ ,  $R_{14}$ ,  $C_3$  and amplifier A<sub>6</sub>, for forcing  $i_b$  to track the current reference. The output of the current regulator,  $v_{o Gc}$ , will be used to provide the term  $k_2'$ in (14) and the error between  $v_m(t)$  and  $v_m_{fit}(t)$ . Subcircuit F is an integrator composed of  $R_{15}$ ,  $C_4$  and amplifier A<sub>7</sub>.  $i_{b ref}$  is sent to this integrator to obtain the first term in (14), defined as  $v_{0 \text{ ff.}}$  Here, the product of  $R_{15}$  and  $C_4$  is designed to be equal to  $1/k_1'$ . Subcircuit G is a differential amplifier, composed of  $R_{16} - C_{19}$  and amplifier A<sub>8</sub>, for realizing the reference current feed-forward control scheme and obtaining the modulation signal  $v_{\rm m}$ .  $v_{\rm m}$  is sent to the controller UC3525, and two drive signals are obtained. The two drive signals are then sent to the corresponding logic circuits, finally generating two complementary drive signals for switches  $Q_{\rm h1}$  and  $Q_{\rm h2}$ .

Subcircuits H and I in Fig. 5 are used for improving the dynamic performance of the PPS when the load is triggered on and terminated, which will be explained in Section IV.

## IV. SOLUTIONS FOR IMPROVING THE DYNAMIC RESPONSE OF THE ACC

## A. Dynamic Performance When the Pulsed Load is Triggered on and Terminated

As mentioned in Section III, the current reference of  $i_b$  is extracted from the pulsed load current via a noninverting amplifier and a one-order HPF. The transfer function of the one-order HPF is

$$G_{\rm HPF}\left(s\right) = \frac{s}{s + 2\pi f_0} \tag{17}$$

where  $f_0$  is the corner frequency of the HPF. The phase-shift introduced by the HPF is

$$\varphi = 90^\circ - \arctan \frac{2\pi f}{2\pi f_0} = 90^\circ - \arctan \frac{f}{f_0}$$

(18)

Therefore, the error between the output and input of the HPF is

$$I_{error} = \frac{I_{o_s} \angle 0 - I_{o_s} \angle \varphi}{I_{o_s} \angle 0} = 2\sin\left(\frac{\varphi}{2}\right)$$

(19)

Combining (18) and (19), the corner frequency of the HPF should be designed less than 1% of the PRF if  $I_{error}$  is required to be smaller than 1% at the PRF. This leads to an extremely slow dynamic response of the HPF.

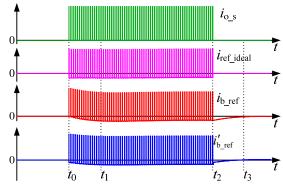

Fig. 6 shows the dynamic waveforms of the HPF, where,  $i_{o_s}$  and  $i_{b_ref}$  are the sensed pulsed load current and current reference for the ACC, respectively,  $i_{ref_ideal}$  is the desired current reference. As seen, when the pulsed load is triggered on at  $t_0$ ,  $i_{b_ref}$  has a dc component during  $[t_0, t_1]$  resulted by the HPF. Thus, the released energy from the ACC is larger than the absorbed energy in one pulse cycle. This will lead to the decrease of  $v_{Cs}$ , and  $v_{Cs}$  will decay to  $V_o$ . Then, the output filter capacitor  $C_f$  starts to release energy. Since  $C_f$  is

Fig. 6. Dynamic waveforms of high pass filter.

relatively small, there will be a large voltage undershoot.

When the pulsed load is terminated at  $t_2$ , the capacitor  $C_b$ in the HPF, as shown in subcircuit A in Fig. 5, is discharged through  $R_b$  during  $[t_2, t_3]$ , and  $i_{b\_ref}$  is still negative. Thus,  $C_s$ will be charged and  $v_{C_s}$  increases. Due to the low bandwidth of the voltage loop, a large voltage overshoot will arise in  $v_{C_s}$ .

From the above analysis, it can be concluded that, when the pulsed load is triggered to work and is terminated, the dynamic response of PPS is poor due to the HPF and low bandwidth of the voltage loop. In order to improve the dynamic performance, several solutions are proposed as follows.

#### B. Solutions for Improving the Dynamic Performance

### 1) Subtracting DC Bias from the Current Reference

The function of the HPF is to remove the dc components  $I_{o_s}$  from  $i_{o_s}$ . If  $i_{o_s}$  is a pure ac component, shown as  $i'_{ref_ideal}$  in Fig. 6, the response time of the HPF would be zero. Hence, if a negative bias  $I_{bias}$  is imposed on  $i_{o_s}$  in advance, the response time of the HPF can be shortened effectively, shown as  $i'_{b_ref}$  in Fig. 6. Subcircuit H in Fig. 5 shows the implementation of this method. The transistor  $Q_1$  is controlled by the pulsed load trigger signal. When the pulsed load is triggered to work at  $t_0$ ,  $Q_1$  is turned off and the negative bias  $I_{bias}$  is imposed. When the pulsed load is terminated at  $t_2$ ,  $Q_1$  is turned on and the bias  $I_{bias}$  is removed.

Nevertheless, the dc component  $I_{o_s}$  varies with the magnitude of the pulsed load. When the magnitude of the pulsed load is low, i.e., at light load,  $I_{o_s}$  is nearly zero. Under this load condition, if  $I_{bias}$  is chosen to be too large, the energy provided by the ACC is insufficient, and  $C_f$  will be discharged when the pulsed load is triggered on, leading to a large voltage undershoot. So, a tradeoff should be made between light load and heavy load conditions when choosing the value of  $I_{bias}$ . Here,  $I_{bias}$  is set to half of the maximum value of  $I_{o_s}$  at full load.

## 2) Peak Voltage Control for the ACC Storage Capacitor Voltage

The dc-dc converter is designed to provide the average power and has no capability of providing the pulsed power. To gain a good dynamic performance, the energy stored in the storage capacitor in the ACC when the pulsed load is at off state should be enough, so as to provide the deficit between the pulsed load and the output power of the dc-dc converter when the pulsed load is triggered on. So, it is better to regulate the peak voltage of the ACC storage capacitor at the desired value. To enforce this, the peak voltage control is used here, and a peak value detection circuit (subcircuit B), as shown in Fig. 5, is added to detect the peak voltage of  $v_{Cs}$ .

#### 3) Limiting of the Maximum and Minimum Voltage of $C_s$

As aforementioned, the bandwidth of the ACC voltage loop is designed much lower than the PRF to mitigate its influence on the reference of the ACC terminal current. This will result in a large overshoot or undershoot in  $v_{Cs}$  when the load is triggered on and terminated, and even causes damage to the power devices in the ACC. To address this issue, two fast voltage loops, which usually adopt a proportional regulator, are introduced to limit the maximum voltage (slightly higher than the nominal value) and minimum voltage (slightly lower than the nominal value), respectively, as shown in Fig. 5 (subcircuit I). When the storage capacitor voltage exceeds the upper limit, the voltage loop used to limit the maximum value will be put into service. When the storage capacitor voltage reaches the lower limit, the voltage loop used to limit the minimum value will put into service. Obviously, the three voltage loops shown in Fig. 5 can transition smoothly among each other.

Likewise, two fast voltage loops can be also be introduced to limit the maximum and minimum voltage for the dc-dc converter.

### V. DESIGN OF THE INDUCTOR IN THE ACC AND THE FILTER CAPACITOR OF THE DC-DC CONVERTER

The design of the dc-dc converter is similar to the regular dc-dc converter except for the output filter capacitor  $C_{\rm f}$ , and it will not be discussed here. In the following, only the design of the inductor in the ACC and the output filter capacitor  $C_{\rm f}$  are given.

#### A. Design of the Inductor in the ACC

In order to reduce the conduction loss of the power switches in the ACC, the current ripple of the inductor in the ACC is preferred to be small. However, too small current ripple means a large inductor, which will leads to a large size and deteriorate the dynamic response. Hence, a tradeoff should be made when designing the inductor. Here, the current ripple is chosen as 20% of the average value.

The inductor in the ACC can be calculated as [20]

$$L_{\rm b} = \frac{\left(V_{C_{\rm s}}(t) - V_{\rm o}\right)V_{\rm o}}{f_{\rm s} \cdot \Delta i_{Lb} \cdot v_{C_{\rm s}}(t)}$$

(20)

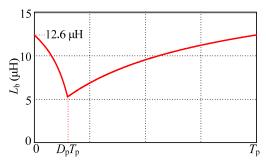

where,  $f_s$  is the switching frequency,  $\Delta i_{Lb}$  is the inductor current ripple. Here, the switching frequency is chosen as 100 kHz. Then, according to (6) and (20), the curve of the inductance in the ACC in one pulse cycle is depicted, as shown in Fig. 7. Hence, we choose the inductor as 12.6µH.

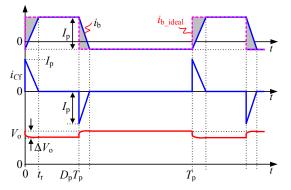

## B. Design of the Output Filter Capacitor

The inductor in the ACC limits the increasing slope of the terminal current of the ACC,  $i_b$ , as shown in Fig. 8. Thus, at the rising edge of the pulsed load current, the output filter capacitor of the PPS,  $C_f$ , is discharged to provide the deficit, causing its voltage to decrease. At the falling edge of the pulsed load current,  $C_f$  is charged to absorb the surplus current, causing its voltage to increase. Note that the voltage drop of  $C_f$  at the rising edge is the voltage drop during the pulse cycle. So, the output filter capacitor  $C_f$  should be properly designed to ensure the voltage drop meets the requirements within the pulse cycle.

Fig. 7. Curve of the inductance in the ACC.

Fig. 8. Waveforms of the ACC terminal current tracking the current reference.

As seen in Fig. 8, at the rising edge of the pulsed load current, the top switch of the ACC,  $Q_{b1}$ , starts to conduct. Thus, the ACC terminal current  $i_b$  increases linearly and it increases to the desired value  $I_p(1-D_p)$  at  $t_r$ .  $t_r$  can be expressed as

$$t_{\rm r} = \frac{L_{\rm b} \cdot \Delta I_{\rm Lb}}{V_{\rm Cs\,max} - V_{\rm o}} = \frac{L_{\rm b} I_{\rm p}}{V_{\rm Cs\,max} - V_{\rm o}}$$

(21)

Letting  $V_{Csmax} = 60$  V and substituting it together with  $L_b = 12.6 \,\mu\text{H}$ ,  $V_o = 28$  V,  $I_p = 71$  A into (21), we have  $t_r = 27.96 \,\mu\text{s}$ .

During  $[0, t_r]$ ,  $C_f$  will be discharged to provide deficit, and the current of  $C_f$  is expressed as

$$i_{\rm Cf}\left(t\right) = I_{\rm p} - \frac{I_{\rm p}}{t_{\rm r}}t \tag{22}$$

The voltage drop of  $C_{\rm f}$  is

$$\Delta V_o(t) = i_{\rm Cf} R_{\rm esr} + \frac{1}{C_{\rm f}} \int_0^t i_{\rm Cf} dt$$

(23)

where,  $R_{esr}$  is the ESR of the output filter capacitor  $C_{f}$ . Substitution of (22) into (23), yields

$$\Delta V_o(t) = -\frac{I_p}{2C_f t_r} t^2 + \left(\frac{1}{C_f} - \frac{R_{esr}}{t_r}\right) I_p t + I_p R_{esr}$$

(24)

According to (24), the maximum output voltage drop during the pulse cycle is

$$\Delta V_o = \begin{cases} \frac{I_p}{2C_f t_r} \left(t_r - C_f R_{esr}\right)^2 + I_p R_{esr} & t_r > R_{esr} C_f \\ I_p R_{esr} & t_r \le R_{esr} C_f \end{cases}$$

(25)

For an electrolytic capacitor, the product of  $R_{esr}$  and  $C_f$  equals to 60  $\mu$ s [31], which is larger than  $t_r$  (= 27.96  $\mu$ s). So, according to (25), the maximum output voltage drop during the pulse cycle is  $\Delta V_o = I_p R_{esr}$ . Considering  $\Delta V_o = 28 \text{ V} \times 3\%$ ,  $I_p = 71 \text{ A}$ , the maximum allowed ESR can be calculated as  $R_{esr} = 11.8 \text{ m}\Omega$ . Therefore,  $C_f = 5 \text{ mF}$  is chosen.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2018.2793187, IEEE Transactions on Power Electronics

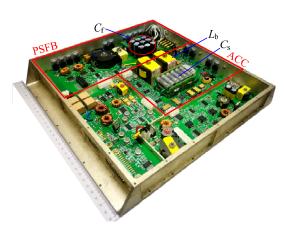

Fig. 9. Photograph of the prototype of the PPS.

Fig. 10. Main circuit of the PPS.

## VI. EXPERIMENTAL VERIFICATION

In order to verify the validity of the proposed PPS adopting the ACC and the control methods, a prototype, shown in Fig. 9, is fabricated and tested in the lab with the specifications listed in Table I. Fig. 10 shows the main circuits of the PPS, where the popular phase-shifted full-bridge (PSFB) converter is adopted as the dc-dc converter. In order to filter the switching-frequency current ripple, an input *LC*-filter composed of  $L_{in}$  and  $C_{in}$  is introduced. Both the PSFB converter and the ACC operate at the switching frequency of 100 kHz. The parameters of the PSFB converter are listed in Table II.

## *A. Volume and Cost Comparison Between the Proposed PPS and Conventional PPS*

In conventional PPS with bulky storage capacitor connects at the output terminal of the PPS, 266 60-V/270- $\mu$ F tantalum capacitors (135D277X0060K6) from Vishay are used for  $C_s$ . When the ACC is adopted, only 18 125-V/82- $\mu$ F tantalum capacitors (135D826X0125K6) from Vishay are needed for  $C_s$ , and another 18 60-V/270- $\mu$ F tantalum capacitors (135D277X0060K6) from Vishay are needed for  $C_f$ . The 60-V/270- $\mu$ F and 125V-82 $\mu$ F tantalum capacitors have the same package. The inductor in the ACC is separated into two inductors connected in series here, and two sets of PTS40 ferrite cores from DMEGC are employed. Four MOSFETs (IPP110N20N3G) from Infineon are selected for the main switches of the ACC, and two MOSFETs are connected in parallel for each switch.

The volume and the cost comparison between two approaches, excluding the PSFB converter, are given in Table III. Note that all the prices for the devices and components are from Mouser Electronics Corporation. As seen, the volume and cost of the ACC are only 25.5% and 13.5% of the storage capacitance connected at the output terminal, respectively. So, the proposed PPS with the ACC has a reduced size and cost compared with the PPS with bulky storage capacitor.

TABLE II

PARAMETERS OF THE PHASE-SHIFTED FULL-BRIDGE CONVERTER

| PSFB converter (100V – 28V, 300W, 100 kHz) |              |                  |       |  |

|--------------------------------------------|--------------|------------------|-------|--|

| Parameters                                 | Value        | Parameters       | Value |  |

| $Q_1 \sim Q_4$                             | IPP600N25N3G | $L_{\mathrm{f}}$ | 21 µH |  |

| $D_{\mathrm{R1}} \sim D_{\mathrm{R2}}$     | MBR20200CT   | $C_{ m f}$       | 5 mF  |  |

| $L_{\rm r}$                                | 6.5 μH       | $L_{in}$         | 40 µH |  |

| $K(N_{\rm p}/N_{\rm s})$                   | 8/3          | $C_{\rm in}$     | 40 µF |  |

TABLE III COMPARISON OF THE VOLUME AND COST BETWEEN THE ACC AND THE BULKY STORAGE CAPACITOR

| Bulky storage capacitors for the PPS |                                     |                             |               |  |  |

|--------------------------------------|-------------------------------------|-----------------------------|---------------|--|--|

| Parameters                           | Туре                                | Volume                      | Cost          |  |  |

| $C_{\rm s}$                          | 135D277X0060K6<br>(60V/270µF) × 266 | 1.93 mL × 266               | \$82.61 × 266 |  |  |

| Total                                |                                     | 0.51 L                      | \$ 22000      |  |  |

| ACC for the PPS                      |                                     |                             |               |  |  |

| Parameters                           | Туре                                | Volume                      | Cost          |  |  |

| $Q_{\rm bl} \sim Q_{\rm b2}$         | IPP110N20N3G $\times$ 4             | $0.29 \text{ mL} \times 4$  | \$ 4.63 × 4   |  |  |

| $C_{ m f}$                           | 135D277X0060K6<br>(60V/270μF) × 18  | 1.93 mL × 18                | \$ 82.61 × 18 |  |  |

| $C_{\rm s}$                          | 135D826X0125K6<br>(125V/82μF) × 18  | 1.93 mL × 18                | \$ 82.61 × 18 |  |  |

| $L_{\rm b}$                          | DMEGC PTS40 $\times$ 2              | $31.42 \text{ mL} \times 2$ | \$ 1.0 × 2    |  |  |

| Total                                |                                     | 0.13 L                      | \$ 2990       |  |  |

#### **B.** Experiment Results

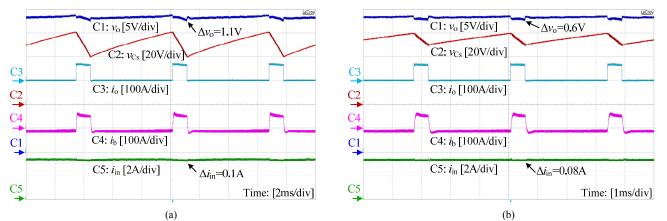

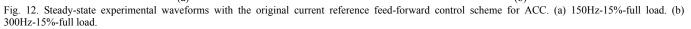

When the ACC adopts the dual-loop control method proposed in [20], the steady-state experimental waveforms with output peak power of 2 kW, pulse duty cycle of 15%, and PRF of 150 Hz and 300 Hz are shown in Fig. 11(a) and (b), respectively, where,  $v_o$  is the output voltage of the PPS,  $v_{Cs}$  is the voltage across  $C_s$ ,  $i_{in}$  is the input current of the PPS,  $i_b$  is the current of  $L_b$ . As seen, the maximum output voltage drop during the pulse cycle is 1.1 V, and the maximum input current ripple is 0.1 A. Obviously, the PSFB converter only provides the average power, which is well in agreement with the theoretical analysis. Furthermore, the maximum value of  $v_{Cs}$  remains the same at different load conditions. Note that, only the waveforms at full load condition are given here since full-load condition is the worst case.

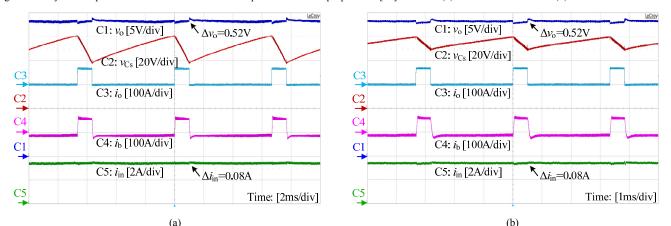

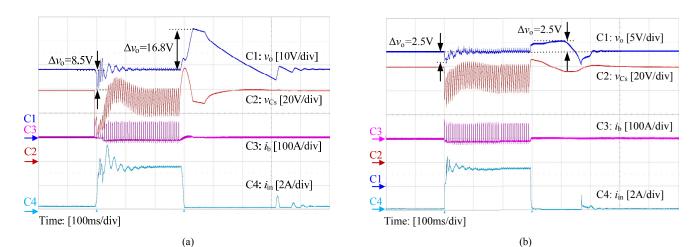

Fig. 12 shows the steady-state experimental waveforms with the original current reference feed-forward control scheme employed for the ACC. It can be seen that maximum output voltage drop during the pulse cycle is 0.52 V and the maximum input current ripple is 0.08 A. By comparing Figs. 11 and 12, it can be seen that the first dip on the output voltage  $V_0$  is nearly the same and it is independent of the PRF. This is because that the inductor in the ACC limits the increasing slope of the terminal current of the ACC, and  $C_{\rm f}$ provides the deficit. However, as seen in Fig. 11, after the first dip, the output voltage is still decaying with the conventional dual-loop control scheme. And the decrease of the output voltage when the PRF is 150 Hz is larger than that when the PRF is 300 Hz. Comparatively, as seen in Fig. 12, after the first dip, the output voltage recovers when the proposed current reference feed-forward control scheme is adopted. This verifies that the proposed current reference feed-forward control scheme can improve the current tracking ability.

Fig. 13 shows the steady-state experimental waveforms

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2018.2793187, IEEE Transactions on Power Electronics

with the simplified current reference feed-forward control scheme for the ACC. As seen, the maximum output voltage drop during pulse cycle is 0.57 V and the maximum input current ripple is only 0.08 A, which is very close to the experimental waveforms shown in Fig. 12. This means the simplification of the feed-forward function does not deteriorate the current tracking ability.

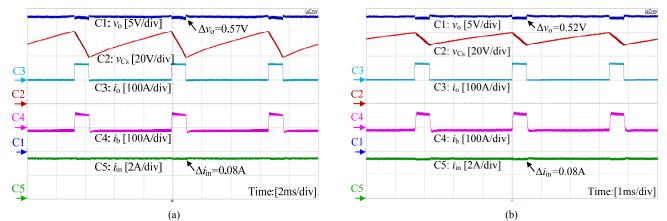

Fig. 14(a) shows the dynamic experimental waveforms when the pulsed load is triggered on and terminated, where, the duty cycle of the pulse is 15% and the PRF is 150 Hz. Here, the peak voltage control is used for the ACC. As seen, the voltage undershoot is 8.5 V when the pulsed load is triggered on and the voltage overshoot is 16.8 V when the pulsed load is terminated. Such a large undershoot and overshoot will weaken the performance of the pulsed load, and even damage the power devices in the PPS. Fig. 14(b)

shows the dynamic experimental waveforms when the load is triggered on and terminated with the methods proposed in Section IV. As seen, both the voltage undershoot and overshoot are about 2.5 V when the pulsed load is triggered on and terminated, respectively, which are significantly reduced compared with that shown in Fig. 14(a). Thus, the dynamic response is greatly improved.

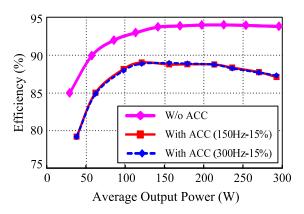

Fig. 15 shows measured conversion efficiency curves of the PPS. As seen, the efficiency of the PPS with the ACC is lower than that of the PPS with bulky storage capacitor. This is due to the additional power loss resulted by the ACC for handling the reactive power and processed reactive power is much higher than the average power of the PPS. However, with the use of ACC, the power density of the PPS is increased and cost is reduced. So, the decrease of the efficiency is acceptable.

Fig. 11. Steady-state experimental waveforms with dual-loop control scheme proposed in [20] for ACC. (a) 150 Hz-15%-full load. (b) 300 Hz-15%-full load.

Fig. 13. Steady-state experimental waveforms with the simplified current reference feed-forward control scheme for ACC. (a) 150Hz-15%-full load. (b) 300Hz-15%-full load.

0885-8993 (c) 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 14. Dynamic experimental waveforms. (a) Only with peak voltage control. (b) With the methods proposed in Section IV-B.

Fig. 15. Conversion efficiency of the PPS.

#### VII. CONCLUSION

In this paper, a boost-type ACC is adopted in place of the bulky storage capacitor for the pulsed power supply (PPS) to provide the pulsed power. By intentionally increasing its voltage ripple, the storage capacitor in the ACC can be significantly compared with the storage capacitance connected at the output terminal. Thus, the size of the PPS is greatly reduced and the power density is greatly increased. A current reference feed-forward control scheme, in which the instantaneous expression of the duty cycle is calculated, is proposed to achieve an excellent current tracking ability for the ACC, and it is further simplified for avoiding the use of multiplier, leading to a simple implementation of the control circuit. Furthermore, to improve the dynamic response of the PPS when the pulsed load is triggered on and terminated, three methods are proposed, including imposing a negative dc bias on the current reference, a peak voltage control for regulating the peak voltage of the ACC storage capacitor, and two fast voltage loops incorporated for limiting the maximum and minimum voltage of the storage capacitor in the ACC. Finally, the experimental results are provided to verify the validity of proposed PPS and control schemes.

#### APPENDIX

This Appendix provides the derivation process of the approximated expression of the function of  $1/\sqrt{x}$ , which is based on the Taylor's expansion method, and the choose of the expansion point of the Taylor's expansion is also given.

By applying Taylor's expansion on  $1/\sqrt{x}$  at  $x = x_0$ , we have

$$\frac{1}{\sqrt{x}} = \frac{1}{\sqrt{x_0}} - \frac{1}{2x_0\sqrt{x_0}} (x - x_0) + \frac{3}{8x_0^2\sqrt{x_0}} (x - x_0)^2 + \cdots$$

$$= \frac{1}{\sqrt{x_0}} \left[ 1 - \frac{1}{2x_0} (x - x_0) + \frac{3}{8x_0^2} (x - x_0)^2 + \cdots \right]$$

(A1)

Neglecting the high-order terms and keeping only the constant term and the first-order term,  $1/\sqrt{x}$  is approximated as

$$\frac{1}{\sqrt{x}} \approx \frac{1}{\sqrt{x_0}} - \frac{1}{2\sqrt{x_0^3}} \left( x - x_0 \right) = -\frac{1}{2\sqrt{x_0^3}} x + \frac{3}{2\sqrt{x_0}}$$

(A2)

The error resulted by the approximation is

$$e(x) = \frac{1}{\sqrt{x}} - \left( -\frac{1}{2\sqrt{x_0^3}} x + \frac{3}{2\sqrt{x_0}} \right)$$

(A3)

By differentiating e(x), we have

$$e'(x) = \frac{1}{2\sqrt{x_0^3}} - \frac{1}{2\sqrt{x^3}}$$

(A4)

As seen in (A4), if  $x > x_0$ , e'(x) > 0; while if  $x < x_0$ , e'(x) < 0. Therefore, the minimum value of e(x) occurs at  $x = x_0$ , and it is zero according to (A3). Thus, we can conclude that  $e(x) \ge 0$ .

According to (A3), integrating e(x) in the range of the value of x, yields

$$e_{\text{int}}(x_0) = \int_{x_{\min}}^{x_{\max}} e(x) dx = 2\left(\sqrt{x_{\max}} - \sqrt{x_{\min}}\right) + \frac{1}{4\sqrt{x_0^3}} \left(x_{\max}^2 - x_{\min}^2\right) - \frac{3}{2\sqrt{x_0}} \left(x_{\max} - x_{\min}\right)$$

(A5)

where  $x_{\min}$  and  $x_{\max}$  are the minimum and maximum values of *x*, respectively. By differentiating  $e_{int}(x_0)$ , we have

$$e_{\rm int}'(x_0) = \frac{3}{4\sqrt{x_0^5}} \left( x_{\rm max} - x_{\rm min} \right) \left( x_0 - \frac{x_{\rm max} + x_{\rm min}}{2} \right)$$

(A6)

As seen in (A6), if  $x_0 > (x_{\max} + x_{\min})/2$ ,  $e_{int}'(x_0) > 0$ ; while if  $x_0 < (x_{\max} + x_{\min})/2$ ,  $e_{int}'(x_0) < 0$ . Therefore, the minimum value of  $e_{int}(x_0)$  occurs when  $x_0 = (x_{\max} + x_{\min})/2$ . That is to say, the fitting accuracy of the approximated expression of  $1/\sqrt{x}$ , as given in (A2) is optimal when

$$x_0 = (x_{\min} + x_{\max})/2$$

(A7)

If x is defined as (11) in Section III-B, we have

$$x_{\min} = V_{Csmin}^2 , \quad x_{\max} = V_{Csmax}^2$$

(A8)

Thus, we have

2

$$c_0 = \left(V_{\rm Csmin}^2 + V_{\rm Csmax}^2\right) / 2 \tag{A9}$$

#### References

- F. J. Beckers, W. F. Hoeben, T. Huiskamp, A. J. Pemen, and E. J. van Heesch, "Pulsed corona demonstrator for semi-industrial scale air purification," *IEEE Trans. Plasma Sci.*, vol. 41, no. 10, pp. 2920–2925, Oct. 2013.

- [2] D. Voncina and J. Nastran, "Current source for pulse plating with high di/dt and low ripple in steady state," in Proc. IEEE Int. Symp. Ind. Electron., 1999. pp. 753–756.

- [3] A. Elserougi, A. M. Massoud, A. M. Ibrahim, and S. Ahmed, "A high voltage pulse-generator based on dc-to-dc converters and capacitor-diode voltage multipliers for water treatment applications," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 22, no. 6, pp. 3290–3298, Dec. 2015.

- [4] H. Akiyama, S. Sakai, T. Sakugawa, and T. Namihira, "Environmental applications of repetitive pulsed power," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 14, no. 4, pp. 825–833, Aug. 2007.

- [5] A. K. Jain, D. McIntosh, M. Jones, and B. Ratliff, "A 2.5 kV to 22 V, 1 kW radar decoy power supply using silicon carbide semiconductor devices," in *Proc. Eur. Conf. Power Electron. Appl.*, 2011, pp. 1–10.

- [6] R. A. Gardenghi and R. C. Houlne, "Power supply consideration for pulsed solid-state radar," in *Proc. IEEE Power Modulator Symp.*, 1990, pp. 146–152.

- [7] H. S. Ginsberg, and L. W. Koenig, "A pulsed load power supply for high performance solid state radar transmitters," in *Proc. IEEE Power Modulator Symp.*, 1994, pp. 20–23.

- [8] C. R. Sullivan, J. J. Awerbuch, and A. M. Latham, "Decrease in photovoltaic power output from ripple: Simple general calculation and the effect of partial shading," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 740–747, Feb. 2013.

- [9] N. Femia, G. Petrone, G. Spagnuolo, and M. Vitelli, "A technique for improving P&O MPPT performances of double-stage grid-connected photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 56, no. 11, pp. 4473–4482, Nov. 2009.

- [10] G. Fontes, C. Turpin, S. Astier, and T. Meynard, "Interactions between fuel cells and power converters: Influence of current harmonics on a fuel cell stack," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 670–678, Mar. 2007.

- [11] Y. R. Novaes and I. Barbi, "Low frequency ripple current elimination in fuel cell systems," in *Proc. Fuel Cell Seminar Special Session on Power Conditioning and International Future Energy Challenge*, 2003, pp. 21–26.

- [12] P. T. Krein, R. S. Balog, and M. Mirjafari, "Minimum energy and capacitance requirements for single-phase inverters and rectifiers using a ripple port," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4690–4698, Nov. 2012.

- [13] M. S. Irfan, A. Ahmed, J. H. Park, and C. Seo, "Current-sensorless power-decoupling phase-shift dual-half-bridge converter for dc-ac power conversion systems without electrolytic capacitor," *IEEE Trans. Power Electron.*, vol. 32, no. 5, pp. 3610–3622, May 2017.

- [14] Y. Sun, Y. Liu, M. Su, W. Xiong, and J. Yang, "Review of active power decoupling topologies in single-phase systems," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4778–4794, July 2016.

- [15] S. H. Pini and I. Barbi, "The single-phase high-power-factor rectifier, based on a two-quadrant shunt active filter," *IEEE Trans. Power Electron.*, vol. 26, no. 11, pp. 3131–3143, Apr. 2011.

- [16] R. Wang, F. Wang, D. Boroyevich, R. Burgos, R. Lai, P. Ning, and K. Rajashekara, "A high power density single-phase PWM rectifier with active ripple energy storage," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1430–1443, May 2011.

- [17] Y. Tang, Z. Qin, F. Blaabjerg, and P. Loh, "A dual voltage control strategy for single-phase PWM converters with power decoupling function," *IEEE Trans. Power Electron.*, vol. 30, no. 12, pp. 7060–7071, Dec. 2015.

- [18] X. Cao, Q. Zhong, and W. Ming, "Ripple eliminator to smooth dc-bus voltage and reduce the total capacitance required," *IEEE Trans. Ind. Electron.*, vol. 62, no. 4, pp. 2224–2235, Apr. 2015.

- [19] S. Li, A. T. L. Lee, S. C. Tan, and S. Y. Hui, "A plug-and-play ripple mitigation approach for dc-links in hybrid systems," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2016, pp. 169–176.

- [20] S. Wang, X. Ruan, K. Yao, S. C. Tan, Y. Yang, and Z. Ye, "A flicker-free electrolytic capacitor-less ac-dc LED driver," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4540–4548, Nov. 2012.

- [21] Y. Yang, X. Ruan, L. Zhang, J. He, and Z. Ye, "A feed-forward scheme for an electrolytic capacitor-less ac/dc LED driver to reduce output current ripple," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5508–5517, Oct. 2014.

- [22] Y. Wen and O. Trescases, "Non-linear control of current-mode buck converter with an optimally scaled auxiliary phase," in *Proc. IEEE Int. Conf. Ind. Technol.*, 2010, pp. 783–788.

- [23] Y. Wen and O. Trescases, "Dc-dc converter with digital adaptive slope control in auxiliary phase for optimal transient response and improved efficiency," in *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3396–3409, July 2012.

- [24] Z. Shan, S. C. Tan, and C. K. Tse, "Transient mitigation of dc-dc converters for high output current slew rate applications," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2377–2388, May 2013.

- [25] X. Zhang, X. Ruan, H. Kim, and C. K. Tse, "Adaptive active capacitor converter for improving stability of cascaded dc power supply system," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1807–1816, Apr. 2013.

- [26] H. Wang and H. Wang, "A two-terminal active capacitor," *IEEE Trans. Power Electron.*, vol. 32, no. 8, pp. 5893–5896, Aug. 2017.

- [27] R. Chen, Y. Liu, and F. Z. Peng, "A solid state variable capacitor with minimum capacitor," *IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5035–5044, July 2017.

- [28] X. Huang, X. Ruan, F. Du, F. Liu, and L. Zhang, "High power and low voltage power supply for low frequency pulsed load," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2017, pp. 2859-2865.

- [29] C. Liu and J. S. Lai, "Low frequency current ripple reduction technique with active control in a fuel cell power system with inverter load," *IEEE Trans. Power Electron.*, vol. 22, no. 4, pp. 1429–1436, July 2007.

- [30] G. Zhu, X. Ruan, L. Zhang, and X. Wang, "On the reduction of second harmonic current and improvement of dynamic response for two-stage single-phase inverter," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 1028–1041, Feb. 2015.

- [31] A. I. Pressman, K. Billings, and T. Morey, *Switching Power Supply Design, 2nd Ed.* J. Peters, Ed. New York, NY, USA: McGraw-Hill, 2009.

Xinze Huang received the B. S. degrees in electrical engineering and automation from Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 2014, where he is currently working toward the Ph.D. degree in electrical engineering.

His current research interests include renewable energy generation systems and cascaded power system.

Xinbo Ruan (M'97-SM'02-F'16) received the B.S. and Ph.D. degrees in electrical engineering from Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 1991 and 1996, respectively.

In 1996, he joined the Faculty of Electrical Engineering Teaching and Research Division, NUAA, where he became a Professor in the College of Automation Engineering in 2002 and has been engaged in teaching and research in the

field of power electronics. From August to October 2007, he was a Research Fellow in the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hong Kong, China. From March 2008 to Sep. 2011, he was also with the School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, China. He is a Guest Professor with Beijing Jiaotong University, Beijing, China, Hefei University of Technology, Hefei, China, and Wuhan University, Wuhan, China. He is the author or co-author of 9 books and more than 200 technical papers published in journals and conferences. His main research interests include soft-switching dc-dc converters, soft-switching inverters, power factor correction converters, modeling the converters, power electronics system integration and renewable energy generation system.

Prof. Ruan was a recipient of the Delta Scholarship by the Delta Environment and Education Fund in 2003 and was a recipient of the Special Appointed Professor of the Chang Jiang Scholars Program by the Ministry of Education, China, in 2007. From 2005 to 2013, he served as Vice President of the China Power Supply Society (CPSS), and from 2017, he serves as Vice President of CPSS again. Since 2008, he has been a member of the Technical Committee on Renewable Energy Systems within the IEEE Industrial Electronics Society. Currently, he serves as an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANSACTIONS ON POWER ELECTRONICS, AND the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS - II. He is an IEEE Fellow.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TPEL.2018.2793187, IEEE Transactions on Power Electronics

**Fangjun Du** received the B. S. and M.S. degrees in electrical engineering from Nanjing University of Aeronautics and Astronautics, Nanjing, China, in 2013 and 2016, respectively.

Since May 2016, he has been with the Power SBG ATD-NJ R&D Center, Lite-On Technology Corp., Nanjing, China. His current research interests include ac-dc converters and dc-dc converters.

Fei Liu received the B.S. degree in electrical engineering from Nanjing University of Aeronautics and Astronautics (NUAA), Nanjing, China, in 2015, where she is currently pursuing the M.S. degree in electrical engineering.

Her main research interests include soft-switching dc-dc converters and input-series output-parallel (ISOP) system.

Li Zhang (S'12) received the B. S. and Ph.D. degrees in electrical engineering from Nanjing University of Aeronautics and Astronautics, Nanjing, China, in 2011 and 2017, respectively. From 2017, he is a postdoctoral research

From 2017, he is a postdoctoral research associate with the Center for Ultra-wide-area Resilient Electric Energy Transmission Networks (CURENT), University of Tennessee, Knoxville, TN, USA. His research interests include dc-dc conversion, inverter control, and renewable energy generation systems.